Single Data Rate

Double Data Rate

Quad Data Rate

Bank Group

LPDDR4x > DDR4

Благодаря меньшему размеру и большей емкости по сравнению с DDR4, память LPDDR4x стала важным элементом в эволюции ультратонких цифровых устройств. Она предлагает увеличенную скорость (без разгона) и занимает меньше места.

Устанавливаемая непосредственно на материнскую плату память LPDDR4x занимает мало места и подключается по коротким проводникам, что обеспечивает улучшенную передачу сигнала.

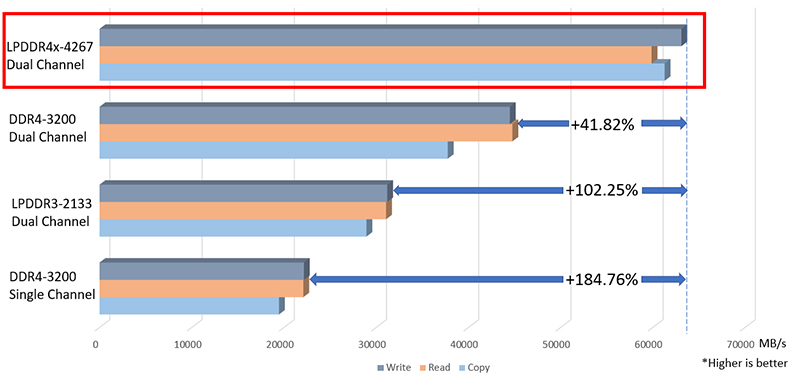

Помимо размера и энергопотребления немаловажным является и вопрос производительности. Память LPDDR4x используется в ноутбуках в двухканальной архитектуре. По сравнению с одноканальным подключением это позволяет снизить длину проводников, что приводит к двойной выгоде: ускоренной передаче данных и меньшему энергопотреблению. Вот почему LPDDR4x-4267 достигает гораздо лучшего результата в тесте AIDA 64 Cache & Memory по сравнению с одноканальной DDR4-3200.

Разделение CK и WCK является сложной задачей, поскольку LPDDR5 SDRAM требует внутренней синхронизации этих сигналов для обработки любой передачи данных на устройство или с устройства. Синхронизация CK с WCK занимает несколько циклов CK, а это означает, что при выполнении операции синхронизации возникает реальный штраф, поэтому будет выгодно по возможности избегать этого. Кроме того, существует определенная последовательность того, как WCK должен вести себя для синхронизации, начиная со статических утверждений по крайней мере для одного CK, за которым следует один CK активности половинной скорости, за которым следует переменное количество CK активности полной скорости на основе рабочая частота. Для рассмотрения примера процедуры нажмите на кнопку Запуск.